主要内容预览:

国家机器的基本概念

国家机器是一种思考方式

我认为,大多数工程专业的学生在学习数字电路时都学会了国家机器的基本概念,并了解一些使用州机器来描述正时电路的基本方法。但是,作者希望每个人都能扩大自己的思维,并意识到国家机器不仅是时间序列的电路设计工具,而且是一种思维方式。

让我们首先看一个简单的例子。在大学生活中,可以简单地将学生的学习生活总结为宿舍,教室和食堂之间的周期,这可以在下面的图片中生动地表达。这张照片不是要讨论学生是否是“好”类型的学生。请注意,如果图片中的“位置”被视为“状态”,并且“函数”被视为状态的“输出”。 ,这张照片是一个标准的州转移图,也就是说,我们使用一台州机来清楚地描述学生在学校的生活方式。

图1-1在学校的学生生活状况转移

图1-2学校的另一个学生的生活状态转移图

同样,如果图中的“位置”被视为“状态”,则“函数”被视为状态的“输出”,并且“条件”被视为状态转变的“输入条件”图6-2也是标准图片状态转移图,通过州机器,我们再次清楚地描述了另一个学生在学校的生活方式。

实际上,使用状态机方法,我们可以详细描述任何学生的生活方式。通过前两个简单的示例,我们发现州机器特别适合描述按顺序发生或具有逻辑规则的事物 - 实际上,这是状态机器的本质。状态机的本质是描述具有逻辑顺序或定期定律的事件的一种方式。该陈述的两个最重要的词是“逻辑顺序”和“时间序列法”。这两个点是国家机器想要描述的核心和优势。换句话说,具有逻辑顺序和时间序列定律的所有事物都适合按照状态机器描述。 。

许多初学者不知道何时应用州机器。这是两个应用程序想法:第一个想法,从状态变量开始。如果电路具有定时定律或逻辑序列,我们可以自然地计划状态,从这些状态开始,分析每个状态的输入,状态过渡和输出,并完成电路函数;第二个想法是首先阐明电路的输出之间的关系,这些输出等同于状态的输出,对每个状态进行反计划以及状态过渡条件和状态输入。不管这个想法是什么,使用状态机的目的是控制电路的某个部分,并完成具有逻辑序列或时机规则的电路设计。

实际上,对于逻辑电路(如简单的定时逻辑,与复杂的微处理器一样大,它们都适用于使用状态机方法的描述。请敞开心放心,不仅限于定时逻辑,发现电路的内部定律,确认电路的“状态变量”,然后大胆地使用状态机来描述电路模型。由于状态机不仅是电路描述工具,因此它也是一种思考方法。此外,状态机器的HDL语言表达相对标准化,并且有规则要遵循,因此许多经验丰富的设计师习惯于使用状态机器进行逻辑设计,将状态机器的设计概念应用于各种复杂的设计,从而提高了效率和设计的稳定性。

国家机器的基本元素和分类

状态机有三个基本元素,即:状态,输出和输入。

根据状态机的输出是否与输入条件有关,状态机可以分为两类:摩尔(摩尔)和Mealy(Mealy)状态机。

根据状态机的数量是否有限,可以将州机器分为有限状态机器(FSM)和无限状态机器(ISM)。通常参与逻辑设计的州是有限的,因此我们将来所说的状态机器是指FSM代表的有限状态机器。

国家机器的基本描述

在逻辑设计中,有三种针对状态机器的基本描述方法,即:状态过渡图,状态过渡列表和HDL语言描述。

状态过渡图是状态机描述的最自然方法。如图1-1和1-2所示,状态过渡图用作描述方法。在设计计划阶段定义逻辑功能时,通常会使用状态传输图,并且在分析代码中的状态机时也可以使用。图形方法有助于理解设计意图。

还值得一提的是,目前有一些EDA工具支持状态过渡图作为逻辑设计的输入,例如statecad。在此工具中,设计师只需要绘制状态传输图即可。 statecad可以自动将状态传输图转换为HDL语言代码,并且翻译的代码是标准化,可读,全面且易于维护的。司法部还可以自动检测状态机器的完整性和正确性,并会警告隐式错误,例如冗余状态,自锁状态,歧义转移条件和状态转移图中的状态机不完整,并协助设计人员纠正错误。 。

最后,司法部将自动生成设计的测试激励措施,并调用模拟程序以验证状态机的正确性。该测试激励措施甚至可以用于仿真后。简而言之,司法部提供了一站式服务,例如国家机器的输入,翻译,检测,优化和测试,使国家机器的设计安全,可靠,快速,方便。这种类型的自动转换状态传输图是HDL源代码工具在设计和分析一些较小的状态机器方面非常有效。但是,由于自动反应代码过于风格化,并且不是最有效的,对于大规模的逻辑设计,通常建议使用HDL语言描述。

使用SYNPLIFY PRO的RTL视图与FSM查看器,您可以在状态过渡图中显示源代码中描述的FSM,并使用图形接口帮助用户分析和理解状态计算机。本文稍后详细介绍了使用FSM查看器分析状态机的方法。

状态传输列表是描述状态机器的列表。它是用于数字逻辑电路的常用设计方法之一。它通常用于简化状态。对于可编程逻辑设计,因为可用的逻辑资源相对较丰富,并且必须考虑状态编码。设计稳定性,安全性和其他因素,因此状态转移列表并不经常用于优化状态。

使用HDL语言描述状态机是本章的重点。使用HDL语言描述状态机具有一定的灵活性,但这绝不是一个狂野的想法,但这是遵循的规则。通过一些标准描述方法,可以使HDL语言中描述的状态机变得更安全,稳定,高效且易于维护。

如何写一台好的状态机器

在RTL级别中,更好的FSM是什么?描述

综合状态机器描述的一些基本规格是如何在RTL级别描述安全有效的FSM。

首先,我们将介绍良好RTL级FSM的评估标准。实际上,有许多判断FSM的标准。在这里,我们将讨论最重要的方面。判断良好RTL级FSM的标准如下:

任何RTL设计都应满足设计的频率要求。

同样,任何RTL设计都应满足设计区域的要求。

其他人很难解释不规则的FSM写作方法,即使过了一会儿,设计师也发现很难维护。

应当指出的是,上述标准,尤其是前三个标准,绝不是分开的,它们是直接相关的。 FPGA/CPLD设计评估的两个基本标准:区域和速度。在这里,“区域”是指设计消耗的逻辑资源数量; “速度”是指设计在芯片上稳定运行时可以达到的最高频率。两者是反对与团结统一的矛盾。要求设计具有最小的设计区域和最高的工作频率是不现实的。科学设计目标应该是:在满足设计时机要求(包括设计的最高频率要求)的前提下占据最小的芯片区域,或者使设计时机余量更大,并且频率更高。

此外,如果要求FSM安全,则通常需要“完整案例”编码方法,也就是说,在FSM中相应地处理了状态转移变量的所有向量组合,这通常意味着花费更多的设计。资源有时会影响FSM的频率。

因此,必须根据设计要求对每个标准进行全面考虑和权衡。但是,如果判决标准之间存在冲突,请考虑列出标准的顺序。上述标准的上市顺序是根据设计中这些标准的重要性安排的,这意味着第一个规则是“ FSM必须是安全的,并且具有很高的稳定性”。 “最高优先级是最重要的;第4条” FSM设计应该清晰,易于理解,易于维护”的优先级最低,这是相对次要的标准。

RTL级状态机器描述的常见语法

本节讨论了Verilog的基本语法和通用关键字。其中,可以在RTL级别设计的与FSM相关的通用关键字如下:

示例:状态计算机使用具有“ 0”初始值的单热编码方法来定义状态变量NS(代表下一个状态,下一个状态)和CS(代表当前状态,当前状态),具有4位宽度定义,状态机包括5个特定状态空闲(空闲状态),S1(工作状态1),S2(工作状态2),S3(工作状态3)和错误(警报状态),代码如下:

reg [3:0] NS,CS;parameter [3:0] //one hot with zero initialIDLE = 3’b0000,S1 = 3’b0001,S2 = 3’b0010,S3 = 3’b0100,ERROR = 3’b1000;

在FSM设计中始终使用三种方法。第一种方法是根据主时钟边缘完成同步正时的状态迁移。示例:状态机可以从当前状态CS迁移到下一个状态NS,如下所示:

//sequential state transitionalways @ (posedge clk or negedge nrst)if (!nrst)CS <= IDLE;elseCS <=NS;

始终使用的第二种用法是基于信号敏感表完成组合逻辑的输出。

始终使用的第三种用法是基于时钟边缘完成同步定时逻辑的输出。

case/endcase是FSM描述中最重要的语法关键字,我们将在此处详细讨论。案例/末端的基本语法结构如下:

case (case_expression)case_item1 : case_item_statement1;case_item2 : case_item_statement2;case_item3 : case_item_statement3;case_item4 : case_item_statement4;default : case_item_statement5;endcase

其中,case_expression是案例的判断条件表达。在FSM描述中,通常是当前状态寄存器;每个case_item是案例语句的分支列表。在FSM描述中,通常是FSM中所有状态的列表,您还可以从中分析国家的编码方法; case_item_statement是输入每个case_item的相应操作。在FSM中,它是与每个状态相对应的状态过渡或输出。如果case_item_statement包含多个操作,则可以使用/结束将其嵌套。多次操作;当所有列出的case_item和case_expression不匹配时,默认值是指示操作的可选关键字。

在FSM设计中,为了提高设计的安全性,设计的FSM被排除在输入死循环之外。通常需要添加默认关键字来描述FSM所需状态的互补状态的操作。此外,Verilog还支持不同的关键字,例如Caseex和Casez,但是由于合成器支持这两个关键字略有不同,因此建议初学者使用完整的案例结构代替Caseex或Casez。

示例:特定FSM的状态转移与情况/末端结构相似,如下所示:

case (CS)IDLE: beginIDLE_out;if (~i1) NS = IDLE;if (i1 && i2) NS = S1;if (i1 && ~i2) NS = ERROR;endS1: beginS1_out;if (~i2) NS = S1;if (i2 && i1) NS = S2;if (i2 && (~i1)) NS = ERROR;endS2: beginS2_out;if (i2) NS = S2;if (~i2 && i1) NS = IDLE;if (~i2 && (~i1)) NS = ERROR;endERROR: beginERROR_out;if (i1) NS = ERROR;if (~i1) NS = IDLE;enddefault: beginDefault_out;NS = ERROR;endendcase

尽管Verilog的案例结构在形式上与诸如C之类的高级语言的案例结构相似,但基本不同。 Verilog的案例结构对应于平行判断的硬件结构。当case_expression与任何case_item匹配时,将忽略其他case_item的判断,并且在执行匹配的case_item_statement后,案例结构将直接从案例结构中跳出。

描述状态计算机的主要目的是用任务/终端封装与不同状态相对应的输出,从而增强代码的可维护性和可读性。示例:使用task/endTask:

task IDLE_out;begin{w_o1,w_o2,w_err} = 3'b000;endendtask

当然,在描述状态计算机(例如/else,分配等)时,也将使用其他一些常用的RTL级语法。它们的功能与一般RTL描述方法一致,并且在此处不会描述。

推荐的状态机说明方法

描述状态机器的关键是要清楚地描述上述几台状态机的元素,即如何执行状态转移;每个状态的输出是什么?状态转移是否与输入条件等相关等。特定描述有多种方法。一些设计师习惯于将整个状态机器写入一个始终的模块,其中描述了状态过渡,并描述了状态输入和输出。该写作方法通常称为单段FSM描述方法;另一种写作方式是使用2个始终模块,其中一个使用同步时间来描述状态过渡。另一个模块使用组合逻辑来判断国家过渡条件并描述国家过渡法。这种写作方式称为两阶段FSM描述方法;另一种写作方法是根据两阶段描述方法开发的。该写作方法使用3个始终模块,并且一个总是使用同步时序来描述状态过渡。第二种使用组合逻辑来判断国家转移条件描述了国家转移规则;第三个始终使用同步正时电路来描述每个状态的输出。这种写作方法称为三阶段写作方法。

一般而言,推荐的FSM说明方法是后两种,即两阶段和三阶段的FSM描述方法。原因是:与其他设计一样,最好使用同步时正式设计来提高设计的稳定性并消除毛刺。一般而言,在实施状态机器后,状态过渡部件与正时电路同步,并且状态过渡条件的判断是组合逻辑。两个阶段公式比一阶段代码更合理的原因是,两阶段代码在不同的程序中分别实现了同步时间和组合逻辑,总是始终程序阻止。这样做的好处不仅是为了促进阅读,理解和维护,而且更重要的是,它有利于合成器代码的优化,以帮助用户添加适当的定时约束,并启用布局和路由以实现设计设计。单段FSM描述不利于正时约束,功能更改,调试等,并且不能很好地表示Miller FSM的输出,从而易于写出闩锁,从而导致逻辑函数错误。

总的来说,为了促进描述当前状态的输出,许多设计师习惯于使用合并逻辑来实现当前状态的输出。但是,这种组合逻辑仍然具有毛刺的可能性,并且不利于约束,也不利于合成器和布局路由器的高性能设计。因此,如果该设计运行时钟节的额外延迟,则需要用寄存器注册状态机的输出。但是,在许多实际情况下,不允许插入存储节拍,可以使用三部分的描述方法来解决。与两阶段公式相比,关键是根据输入条件在先前状态下的状态过渡法判断当前状态的输出,以便实现寄存器输出而不插入额外的时钟节拍。

为了易于理解,我们通过一个示例讨论了这三种不同的写作方法。

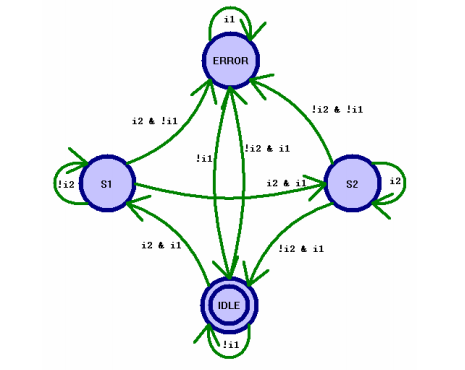

[示例1-1]使用不同的FSM描述样式来描述状态机。在此示例中,我们将使用一个阶段,两个阶段和三阶段公式分别描述图1-3所示的状态机。在这里,我们选择了一台非常典型的Miller状态机,共有4个状态:IDEL,S1,S2,错误;输入信号是时钟clk,低级异步复位信号NRST,输入信号i1,i2,输出信号为O1,O2和ERR,状态关系如图1-2所示。状态的输出如下:

空闲状态的输出为:{o1,o2,err} = 3'b000;

S1状态的输出为:{o1,o2,err} = 3'b100;

S2状态的输出为:{o1,o2,err} = 3'b010;

错误状态的输出为:{o1,o2,err} = 3'b111。

图1-3示例状态过渡图

单段状态机器描述方法(应该避免的写作方法)

此示例的单段描述代码如下:

//1-paragraph method to describe FSM//Describe state transition, state output, input condition in 1 always blockmodule state1 ( nrst,clk,i1,i2,o1,o2,err);input nrst,clk;input i1,i2;output o1,o2,err;reg o1,o2,err;reg [2:0] NS; //NextStateparameter [2:0] //one hot with zero idleIDLE = 3'b000,S1 = 3’b001,S2 = 3’b010,ERROR = 3’b100;//1 always block to describe state transition, state output, input conditionalways @ (posedge clk or negedge nrst)beginif (!nrst)beginNS <= IDLE;{o1,o2,err} <= 3'b000;endelsebeginNS <= 3'bx;{o1,o2,err} <= 3'b000;case (NS)IDLE: beginif (~i1) begin{o1,o2,err}<=3'b000;NS <= IDLE; endif (i1 && i2) begin{o1,o2,err}<=3'b100;NS <= S1;endif (i1 && ~i2) begin{o1,o2,err}<=3'b111;NS <= ERROR;endendS1: beginif (~i2) begin{o1,o2,err}<=3'b100;NS <= S1; endif (i2 && i1) begin{o1,o2,err}<=3'b010;NS <= S2; endif (i2 && (~i1)) begin{o1,o2,err}<=3'b111;NS <= ERROR;endendS2: beginif (i2) begin{o1,o2,err}<=3'b010;NS <= S2; endif (~i2 && i1) begin{o1,o2,err}<=3'b000;NS <= IDLE; endif (~i2 && (~i1))begin{o1,o2,err}<=3'b111;NS <= ERROR;endendERROR: beginif (i1) begin{o1,o2,err}<=3'b111;NS <= ERROR;endif (~i1) begin{o1,o2,err}<=3'b000;NS <= IDLE; endendendcaseendendmodule

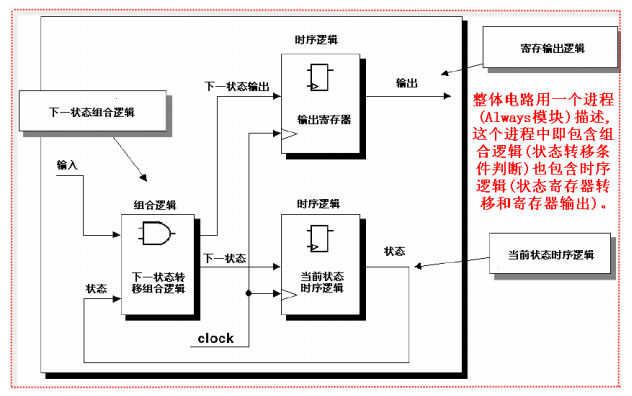

如前所述,单参数的写作方法是同步状态,状态输出和状态的输入条件是用始终模块编写的。单参数的写作方法可以按照图1-4中描述的结构进行总结。

图1-4段FSM描述结构图

一个段描述方法使状态过渡判断的组合逻辑和状态寄存器转换的时机逻辑在同一模块中不符合分别描述时序和组合逻辑的编码样式(代码样式),并且描述当前状态时,应考虑下一个状态的输出。整个代码尚不清楚,这不利于维护和修改,并且不利于其他约束,也不利于合成器和布局路由器对设计的优化。此外,相对于两段描述,此描述相对较长。为了促进初学者掌握,此示例选择了一台非常简单的米勒州立机器,该机器对长期单阶段一阶段的一阶段一阶段的一阶段一阶段的一阶段的一阶段一阶段的一阶段一阶段的一阶段一阶段一阶段一阶段无法做出很好的反应一阶段一阶段一阶段一阶段一阶段一阶段一阶段一阶段一阶段一阶段一阶段一阶段一阶段一阶段一阶段一阶段一阶段一阶段一阶段一阶段一阶段一阶段一阶段一阶段的一阶段一阶段一阶段一阶段一阶段一阶段一阶段一阶段一阶段一阶段一阶段一阶段一阶段一阶段一阶段一阶段一阶段一阶段一阶段一阶段一阶段一阶段一级阶段单阶段一阶段的单阶段单阶段一阶段一阶段一阶段一阶段一阶段一阶段一阶段一阶段一阶段一阶段一阶段一阶段一阶段一阶段一阶段一阶段一阶段一阶段一阶段 - 阶段一阶段一阶段的一阶段一阶段一阶段一阶段的单阶段一阶段一阶段一阶段一阶段一阶段一阶段一阶段一阶段一阶段的一个阶段约为80%至150%。因此,单段FSM描述是不建议的FSM描述方法,请务必避免使用它。

两阶段状态机器描述方法(推荐写作方法)

为了使FSM描述清晰,简洁,易于维护,易于附加正时约束,并更好地优化合成器和布局路由器,建议使用两阶段的FSM说明方法。该示例的两部分描述代码如下:

//2-paragraph method to describe FSM//Describe sequential state transition in 1 sequential always block//State transition conditions in the other combinational always block//Package state output by task. Then register the outputmodule state2 ( nrst,clk,i1,i2,o1,o2,err);input nrst,clk;input i1,i2;output o1,o2,err;reg o1,o2,err;reg [2:0] NS,CS;parameter [2:0] //one hot with zero idleIDLE = 3'b000,S1 = 3’b001,S2 = 3’b010,ERROR = 3’b100;//sequential state transitionalways @ (posedge clk or negedge nrst)if (!nrst)CS <= IDLE;elseCS <=NS;//combinational condition judgmentalways @ (CS or i1 or i2)beginNS = 3'bx;ERROR_out;case (CS)IDLE: beginIDLE_out;if (~i1) NS = IDLE;if (i1 && i2) NS = S1;if (i1 && ~i2) NS = ERROR;endS1: beginS1_out;if (~i2) NS = S1;if (i2 && i1) NS = S2;if (i2 && (~i1)) NS = ERROR;endS2: beginS2_out;if (i2) NS = S2;if (~i2 && i1) NS = IDLE;if (~i2 && (~i1)) NS = ERROR;endERROR: beginERROR_out;if (i1) NS = ERROR;if (~i1) NS = IDLE;endendcaseend//output tasktask IDLE_out;{o1,o2,err} = 3'b000;endtasktask S1_out;{o1,o2,err} = 3'b100;endtasktask S2_out;{o1,o2,err} = 3'b010;endtasktask ERROR_out;{o1,o2,err} = 3'b111;endtaskendmodule

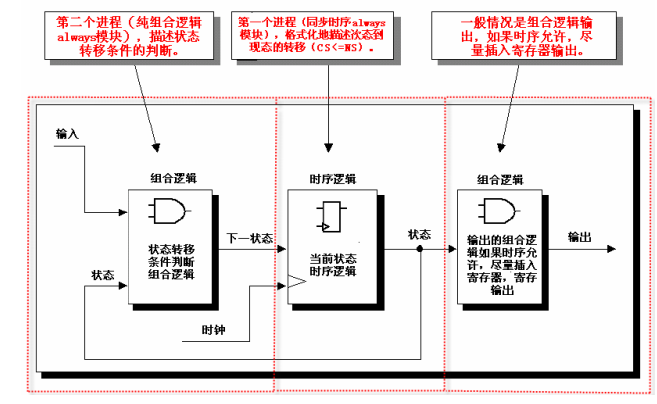

两参数写作方法是推荐的FSM描述方法之一。在这里,我们将仔细讨论代码结构。两阶段FSM的核心是:一个总是使用同步时序来描述状态过渡;另一个模块使用组合逻辑来判断国家过渡条件并描述国家过渡法。两参数写作方法可以汇总如图1-5所述的结构。

图1-5两个阶段FSM描述结构图

在此示例中,描述同步时序状态转换的始终模块代码如下:

always @ (posedge clk or negedge nrst)if (!nrst)CS <= IDLE;elseCS <=NS;

实际上,这是一种程式化的描述结构。无论FSM设计是特定的,都可以定义两个状态寄存器“ CS”和“ NS”,分别代表当前状态和下一个状态,然后根据所需的重置方法。 (同步重置或异步重置),当时钟边缘到达时,将NS分配给CS。应当注意,此同步定时模块的分配必须是非阻滞分配。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请联系本站,一经查实,本站将立刻删除。如若转载,请注明出处:http://www.inakayakusama.com/html/tiyuwenda/9358.html